“딥러닝 하드웨어 가속기 IP 구현 기간 절반으로”

관련링크

본문

“Catapult HLS 방법론 통해 다수의 아키텍처를 모색하고 심층 신경망 가속기를 최적으로 구현하는 방법 찾아내”

전자 설계 자동화(EDA) 소프트웨어 분야의 선도업체인 한국 멘토, 지멘스 비즈니스(대표 김준환)는 칩스앤미디어(Chips&Media)가 멘토의 설계 검증 솔루션인 ‘캐타펄트 HLS(Catapult™ High-Level Synthesis Platform)’을 도입함으로써 심층 신경망(DNN) 알고리즘을 이용해 객체의 실시간 검출을 위한 자사의 c.WAVE100 컴퓨터 비전 IP를 설계 및 검증했다고 발표했다.

칩스앤미디어는 자동차, 감시 및 가전과 같은 시장에 널리 사용되는 SoC 디자인용의 고성능, 고품질 비디오 IP의 주요 공급사이다.

칩스앤미디어는 차별화된 머신러닝 IP를 고객에게 신속하게 제공하기 위해 기능 검증 시간, 타이밍 클로저, 설계 및 아키텍처 최적화를 앞당김으로써 생산성을 극적으로 높여야 했다. 이를 통해 머신러닝 알고리즘과 아키텍처의 연구개발에 더 많은 시간을 투자할 수 있기 때문이다.

이러한 목표를 달성하기 위해 수작업으로 코딩하던 기존의 RTL(register transfer level) 플로우에서 벗어나 Catapult HLS Platform을 채택함으로써 알고리즘과 테스트벤치를 C 언어로 코딩했다. HLS 설계 및 검증 팀은 동일한 프로젝트에 RTL 플로우를 이용한 팀보다 프로젝트 기간을 절반으로 단축했다.

칩스앤미디어 최고기술책임자(CTO)인 전민용 상무는 “특히 추론을 겨냥한 장치에서 DNN 가속 문제를 해결하기 위해서는 개발된 신경망 알고리즘을 전력, 성능 및 면적(PPA)에 집중해 고도로 최적화된 하드웨어 아키텍쳐를 확보하는 것이 열쇠라고 생각한다. 자사는 멘토 HLS를 활용하여 이를 매우 효율적으로 해낼 수 있었다”며 “우리의 프로젝트는 매우 성공적이었다. 향후 프로젝트에도 Catapult를 이용한 HLS 플로우를 채택할 계획이다”고 말했다.

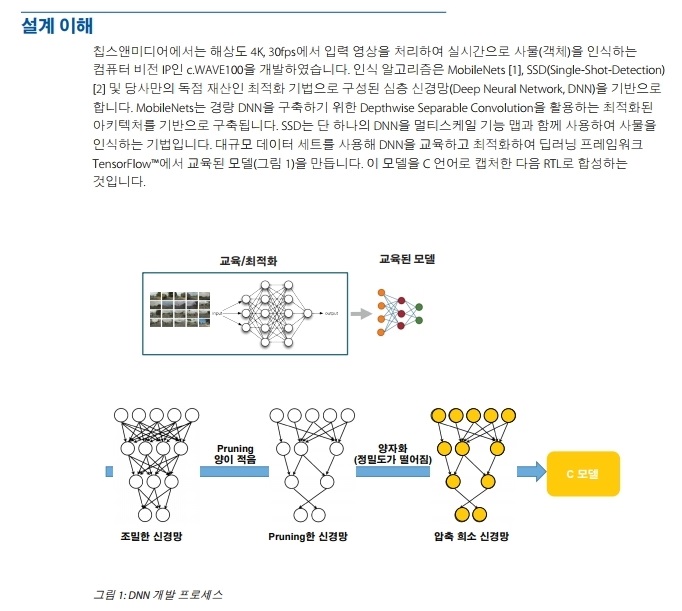

DNN 기반 컴퓨터 비전 프로세싱의 특징 중에는 곱셈/덧셈/누적 연산의 반복적인 계산이 포함되며, 대량의 데이터 이동이 신경망 층을 통해 이루어진다. DNN은 TensorFlow또는 Caffe와 같은 프레임워크 상에서 개발되며, 이어서 해당 알고리즘을 C 모델에서 캡처할 수 있다.

칩스앤미디어는 이 알고리즘 C 모델을 합성 가능한 C 코드로 개선하고, Catapult HLS Platform을 이용해 다양한 아키텍처를 신속하게 모색하고 RTL로 합성함으로써 이러한 유형의 디자인에 최적화된 솔루션을 찾아냈다.

멘토의 디지털 설계 및 구현 솔루션 부문 제너럴 매니저인 바드루 아가왈라(Badru Agarwala)는 “급격한 시장변화가 일어나고 있는 여러 애플리케이션 분야에서 Catapult HLS는 성공에 요구되는 수준의 생산성을 달성할 수 있는 유일한 방법으로서 채택되는 추세”라며 “멘토는 Chips&Media가 HLS로 원활하게 전환할 수 있도록 긴밀하게 협력해왔다. 그 결과 Chips&Media는 하드웨어 RTL구현 및 디버깅 세부사항이 아니라 자신들의 전문기술 분야인 알고리즘/아키텍처 설계에 집중할 수 있었으며, 자신들의 아이디어를 훨씬 더 신속하게 시장에 제공할 수 있었다”고 말했다.

댓글목록

등록된 댓글이 없습니다.